导读 周五,JEDEC协会发布了第四代高带宽内存(HB)的初步规范,距离完成HBDRAM标准已越来越近。据报道,新规范支持每堆栈2048位接口,数据传输速...

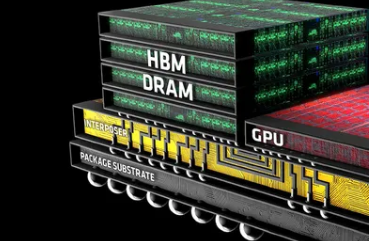

周五,JEDEC协会发布了第四代高带宽内存(HB)的初步规范,距离完成HBDRAM标准已越来越近。据报道,新规范支持每堆栈2048位接口,数据传输速率低于HBM3E。此外,HB支持更广泛的内存层,使新内存能够更好地满足不同类型的应用需求。

新的HB标准将指定24Gb和32Gb层,并提供4高、8高、12高和16高TSV堆栈配置。委员会已初步同意将速度箱设置为高达6.4GT/s,目前正在讨论如何实现更高的数据传输速率。

基于32Gb层的16-Hi堆栈将提供GB的容量,这意味着具有四个内存模块的处理器可以使用8,192位接口支持256GB内存,峰值带宽为6.56TB/s。

尽管与HBM3相比,HB的每个堆栈通道数将增加一倍,并且物理占用空间更大以确保兼容性,但单个控制器可以同时使用HBM3和HB。但是,需要不同的中介层来适应不同的占用空间。值得注意的是,JEDEC并未提及将HBM4内存直接集成到处理器上,而这或许是这种新型内存最吸引人的地方。

今年早些时候,SK海力士和台积电宣布合作开发HB基础。后来,在2024年欧洲技术研讨会上,台积电确认将使用其12FFC+(12nm级)和N5(5nm级)工艺技术来制造这些。

台积电的N5工艺可实现更多集成逻辑和功能,互连间距从9微米到6微米,这对于片上集成至关重要。12FFC+工艺源自台积电的16nmFinFET技术,将能够生产具有成本效益的基片,使用硅中介层将内存连接到主机处理器。

HB主要是为了满足生成式AI和高性能计算的需求而设计的,这些领域需要处理大量数据集并高效执行复杂计算。因此,我们很少会在显卡等客户端应用上看到HB。

跳动城乡网

跳动城乡网